# CHARACTERIZATION OF ELECTRICAL CONTACTS FOR PHASE CHANGE MEMORY CELLS

Deepu Roy

#### Graduation committee:

Chairman:

prof.dr.ir. P. Veltink University of Twente

Secretary:

prof.dr.ir. P. Veltink University of Twente

Promotor:

prof.dr.ir. R.A.M. Wolters University of Twente

Referee:

dr. D.J. Gravesteijn

dr.ir. J.H. Klootwijk

NXP Semiconductors

Philips Research

Internal members:

prof.dr. J. Schmitz University of Twente prof.dr.ir. H. Hilgenkamp University of Twente

External members:

prof.dr.ir. B.J. Kooi University of Groningen prof.dr.ir. R. Dekker Technical University Delft

This research was carried out under project number MC3.07298 in the framework of the research Program of the Materials innovation institute (M2i) in the Netherlands (www.m2i.nl).

This research work was carried out at NXP Semiconductors, Eindhoven, The Netherlands.

PhD Thesis: University of Twente, Enschede, The Netherlands

Title: Characterization of electrical contacts for phase change memory cells

ISBN: 978-90-77172-77-3 Author: Deepu Roy

E-mail: deepuroyjohn@gmail.com Printed by: Proefschriftmaken.nl

Cover image: Water drops falling onto water. This illustrates charge carriers flowing from the phase change materials into the metal electrode at the contact.

## CHARACTERIZATION OF ELECTRICAL CONTACTS FOR PHASE CHANGE MEMORY CELLS

#### DISSERTATION

to obtain

the degree of doctor at the University of Twente,

on the authority of the rector magnificus,

prof.dr. H. Brinksma,

on account of the decision of the graduation committee,

to be publicly defended

on Wednesday the 28<sup>th</sup> of September 2011 at 16:45

by

Deepu Roy, born on the  $28^{\rm th}$  of May 1982 Ezhipuram, Kerala, India. This dissertation is approved by the promoter: prof.dr.ir. R.A.M. Wolters

ISBN: 978-90-77172-77-3

Copyright © 2011 by Deepu Roy

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without written permission of the author.

Printed in The Netherlands

## **Contents**

| 1        | Inti | roduction                                                | 1  |

|----------|------|----------------------------------------------------------|----|

|          | 1.1  | Semiconductor memory technology                          | 2  |

|          | 1.2  | Phase change random access memory                        | 3  |

|          | 1.3  | Scope of this work                                       |    |

|          | 1.4  | Outline of the thesis                                    |    |

| <b>2</b> | Cor  | ntact resistance methodology                             | 7  |

|          | 2.1  | Contact resistance                                       | 8  |

|          | 2.2  | Current transport at the interface                       | 9  |

|          | 2.3  | DC contact resistance measurement structures             | 12 |

|          |      | 2.3.1 Kelvin resistor structures                         |    |

|          |      | 2.3.2 Transfer Length Method (TLM) structures            | 14 |

|          | 2.4  | High frequency measurement structures                    | 21 |

|          | 2.5  | Comparison of the test structures                        | 22 |

|          | 2.6  | Van der Pauw structures                                  |    |

| 3        | Pha  | ase change material properties                           | 25 |

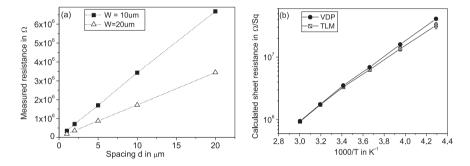

|          | 3.1  | Phase change resistivity measurements                    | 26 |

|          | 3.2  | Optical properties of phase change materials (PCM)       | 28 |

|          | 3.3  | Hall effect measurements on PCM                          | 30 |

|          | 3.4  | Summary                                                  | 33 |

| 4        | Ele  | ctrical characteristics of electrode to PCM contacts     | 35 |

|          | 4.1  | Comparison of TiW to PCM contact resistance measurements | 36 |

|          |      | 4.1.1 Kelvin resistor measurements                       | 36 |

|          |      | 4.1.2 Transfer Length Method measurements                | 38 |

|    |       | 4.1.3 Comparison of Kelvin and TLM measurements             | 40  |

|----|-------|-------------------------------------------------------------|-----|

|    |       | 4.1.4 Temperature dependence of contact resistance          | 41  |

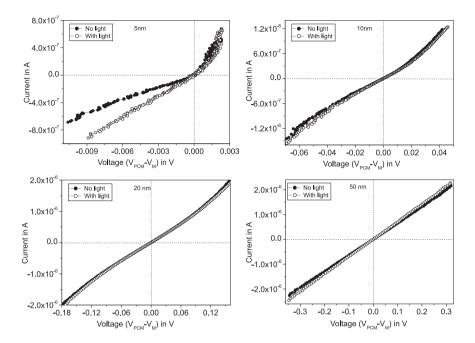

|    |       | 4.1.5 Bias dependence of the contact resistance             | 43  |

|    |       | 4.1.6 Contact resistance with bias and temperature          | 44  |

|    | 4.2   | Contact resistance with different metal electrodes          | 46  |

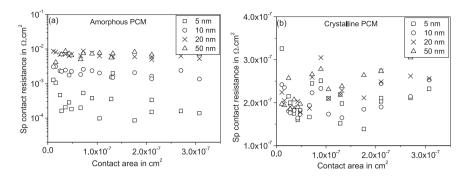

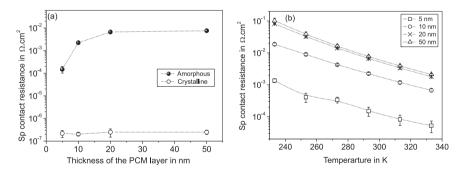

|    | 4.3   | Contact resistance of ultrathin PCM layers                  | 54  |

|    | 4.4   | Conclusions                                                 | 58  |

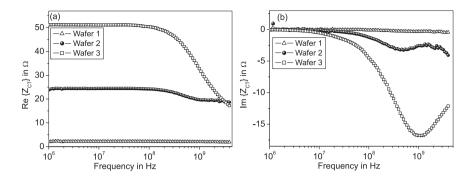

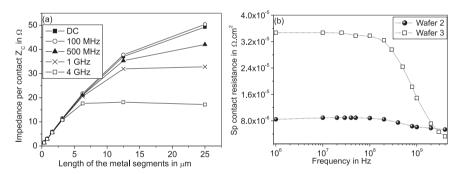

| 5  | Hig   | h frequency contact resistance measurements                 | 61  |

|    | 5.1   | Relevance of high frequency contact resistance measurements | 62  |

|    | 5.2   | Test structure and measurements                             | 63  |

|    | 5.3   | Scott-TLM measurements                                      | 66  |

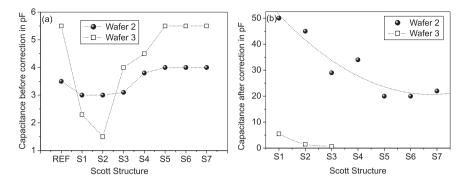

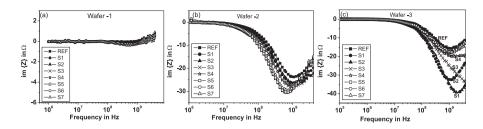

|    |       | 5.3.1 DC measurements                                       | 66  |

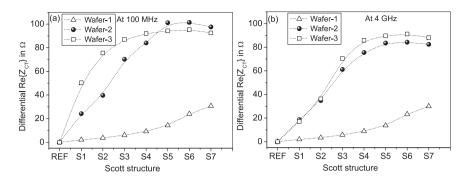

|    |       | 5.3.2 High frequency measurements                           | 67  |

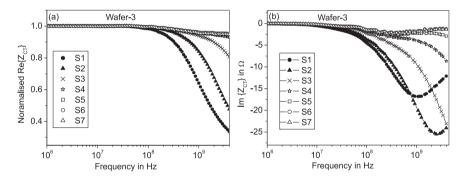

|    |       | 5.3.3 Contact model                                         | 69  |

|    |       | 5.3.4 Measurement limits                                    | 72  |

|    | 5.4   | Linear-TLM measurements                                     | 75  |

|    | 5.5   | Summary and conclusions                                     | 78  |

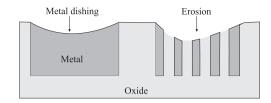

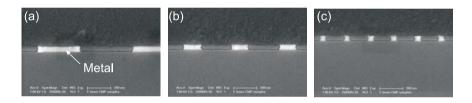

| 6  | Infl  | uence of parasitic current paths on resistance measurements | 81  |

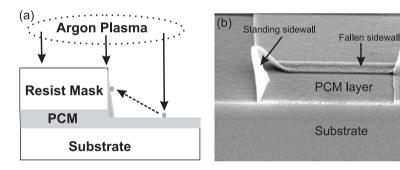

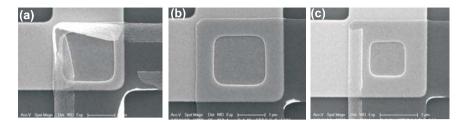

|    | 6.1   | Thin-film structures with re-deposited sidewalls            | 82  |

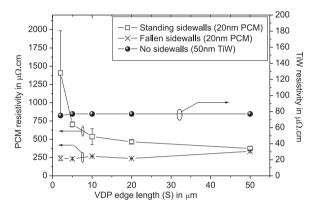

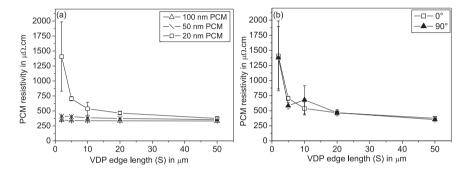

|    |       | 6.1.1 Van der Pauw resistance measurements                  | 83  |

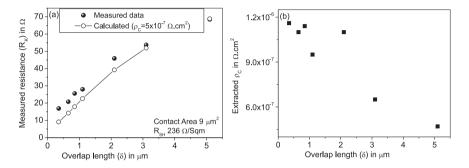

|    |       | 6.1.2 CBKR contact resistance measurements                  | 86  |

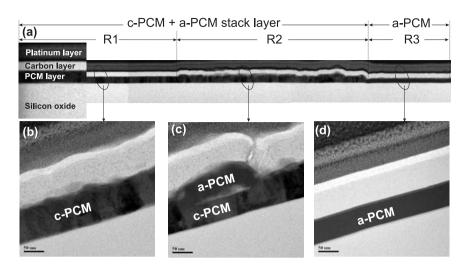

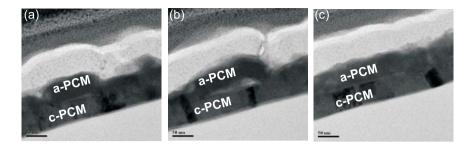

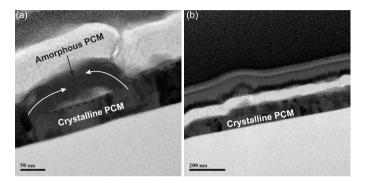

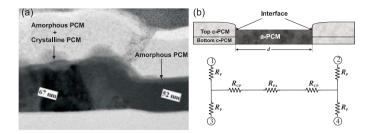

|    | 6.2   | Amorphous PCM to crystalline PCM contact resistance         | 88  |

|    |       | 6.2.1 Kelvin resistor measurements                          | 91  |

|    |       | 6.2.2 TEM analysis                                          | 91  |

|    |       | 6.2.3 TLM measurements                                      | 94  |

|    | 6.3   | Conclusion                                                  | 95  |

| 7  | Cor   | iclusions and Recommendations                               | 97  |

|    | 7.1   | Summary and conclusions                                     | 98  |

|    | 7.2   | Recommendations                                             | 100 |

| A  |       |                                                             | 101 |

|    | A.1   | Contact interface model                                     | 101 |

|    | A.2   | Transmission Line Model                                     | 102 |

|    | A.3   | Hall effect measurements on $p$ -type and $n$ -type silicon | 103 |

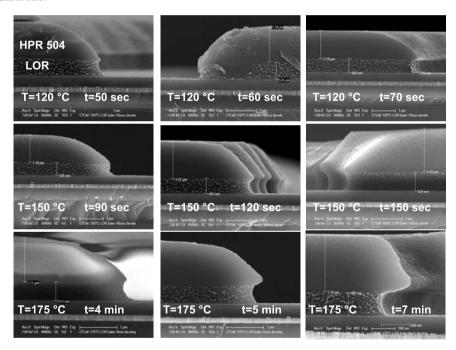

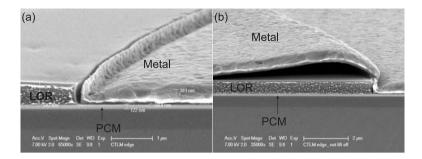

|    | A.4   | Metal lift off process steps                                | 104 |

|    | A.5   | I-V-T measurements                                          | 106 |

|    | A.6   | Test structure fabrication; process-flow                    | 107 |

| Bi | bliog | graphy                                                      | 108 |

| Sa | men   | vatting                                                     | 119 |

|    |       | -                                                           |     |

|                                   | ix  |

|-----------------------------------|-----|

| Summary                           | 121 |

| Acknowledgments                   | 123 |

| Author biography                  | 127 |

| List of publications              | 129 |

| List of symbols and abbreviations | 131 |

# 1

#### Introduction

Phase change random access memory is an emerging candidate as a potential replacement for transistor based flash memories. The objective of this work is to characterize and model the electrical contacts present in these memory cells. The contact properties have a significant influence on the electrical performance, scaling and reliability of these devices.

This chapter begins with an introduction to the different types of emerging semiconductor memory technologies and phase change random access memory in detail. The significance of this research work for phase change memories is discussed in the second session. The organization of this thesis dealing with the characterization of the different aspects of these contacts is also presented.

## 1.1 Semiconductor memory technology

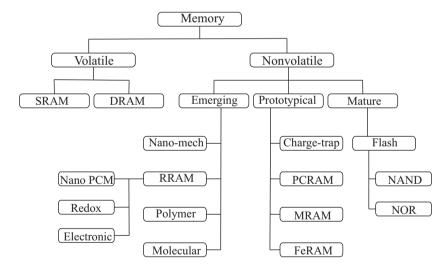

Semiconductor memory is an electronic digital data storage device fabricated in a complementary metal oxide semiconductor (CMOS) based circuitry [1][2]. A type of non-volatile memory that can be erased in large blocks is called the flash memory, which drives the scaling in the memory industry [3]. Flash memories are being used in cellular phones, digital cameras, audio players, universal serial bus (USB) memories, smart cards and many other devices [4]. The advances in consumer electronics and mobile devices demand an increasing requirement for a non-volatile memory with improved performance and better opportunities for dimensional scaling. This leads to the quest for a unified scalable memory for future integrated circuits that combines the required properties of several memory technologies [5][6][2]. They should be scalable and at the same time have the lowest cost per bit. It should have the non-volatile nature of flash, endurance (read and write performance) and speed of DRAM and SRAM. In addition, this memory technology should be compatible with embedded (CMOS technology) and stand alone application with multibit-storage and 3D integration potential. Several novel memory concepts have been researched over the past years to qualify these requirements. The latest classification of present and future semiconductor memory devices as projected by the International Technology Roadmap for Semiconductors (ITRS) is given in Fig. 1.1 [2]:

Figure 1.1: Classification of semiconcductor memory technology by ITRS.

For the short term (2016-2021 time frame) phase change random access memory (PCRAM), magnetic random access memory (MRAM) and ferroelectric random access memory (FeRAM) are being considered as a potential replacement for present day flash memories.

## 1.2 Phase change random access memory

In phase change memory cells, information is stored as the amorphous or crystalline state of the integrated phase change material [7][8]. These materials are compounds or alloys which contain one element from group VI of the periodic table. They are widely used as the active material in compact disc- rewritable (CD-RW) and digital versatile disc-rewritable (DVD-RW), where the optical reflectivity difference of the two states is used to store information [9]. In this case programming and read out is achieved by laser pulse operation. In PCRAM cells the difference in resistance between the states is employed to achieve the memory functionality. The crystalline state has a two to three orders of magnitude lower electrical resistivity than the amorphous state. Switching is achieved by electrical pulse operation. In this study, the commonly used materials based on antimony (Sb) and tellurium (Te), Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> and doped-Sb<sub>2</sub>Te, are investigated. Electrically controlled switching of PCM was first reported by Ovshinsky in 1968 [10]. Later the first 256 bit phase change memory array was demonstrated in 1970 by R. G Neale, D. L. Nelson and Gordon E. Moore [11]. This memory cell consisted of a PCM resistive storage element in series with a silicon based p-n diode as an access device. Even though the concept was developed and prototypical devices were fabricated, the memory industry did not follow the phase change memory technology because of the large power required to program these cells. The reset energy at that time was 25  $\mu$ J/bit. This energy required to program depends on the volume of PCM in the cell.

As the semiconductor industry faithfully followed Moore's law<sup>1</sup>, lithographic tools were developed that can define smaller feature sizes. With this shrink in the feature size, the volume of the material in the PCRAM cell decreased with cubic progression. Reaching the 180 nm technology node, the power required to program a phase change memory cell is demonstrated to be feasible to be used in electronic devices [8]. This power consumption for PCRAM cell will decrease as the device size is further scaled down [13]. The write energy is now in the range of 5 pJ/bit [2].

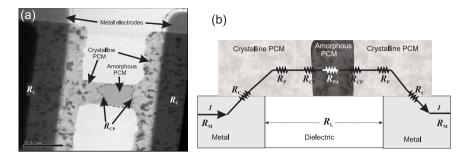

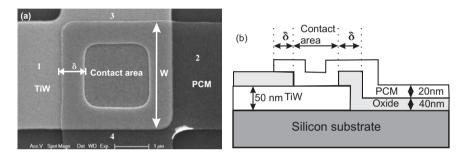

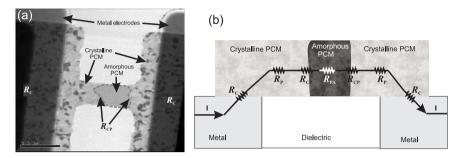

An embedded PCRAM cell consists of a thin-film PCM layer integrated in the metallization level of an integrated circuit in combination with an access device. Different integration schemes have been proposed [3][8][14] following the original Ovonic Unified Memory (OUM) concept [15]. The cell architecture introduced by NXP Semiconductors is the *line* cell concept. Here a thin line of PCM is placed between two metal electrode contacts [5]. A top-view transmission electron microscope (TEM) image of such a line cell switched to the amorphous state is shown in Fig. 1.2(a). The memory storage or programmable part of the PCM is the line that is switched between amorphous and crystalline states [7]. The schematic cross section of which is shown in Fig. 1.2(b).

Programming operation of the memory cell from high resistance (Fig. 1.2(a))

<sup>&</sup>lt;sup>1</sup>The number of devices in a given chip area roughly doubles every year [12].

Figure 1.2: (a) Top-view TEM image of the PCM line cell. (b) Schematic cross section of the line showing the switching region, including the electrical schematic.

to low resistance (set operation) is achieved by threshold switching ( $V_{\rm TH}$ ) and subsequent thermal annealing (typically at 250 °C of the disordered amorphous material part into the ordered crystalline state [8][5]. Thermal steps are achieved by Joule heating using electrical pulses from the accompanying transistor. Switching of the memory cell from low resistance (crystalline) to high resistance (amorphous) (reset operation) involves the heating of the PCM by higher electrical pulses above the melting point at typically 650 °C and cooling it quickly (quenching). The material remains in the amorphous melt-quenched state. Set, reset and read out are done by the same transistor using different electrical pulses.

The resistance of the cell in the set (crystalline) state  $R_{\rm set}$  is determined by the PCM line resistance ( $R_{\rm L}$ ), contact resistance ( $R_{\rm C}$ ) and the metal resistance ( $R_{\rm M}$ ), as depicted in Fig. 1.2(b). In the reset state, the resistance of the line cell  $R_{\rm reset}$  is mainly determined by the amorphous PCM present in the cell. In other cell configurations also the contact resistance of metal electrodes to amorphous PCM is involved.

#### 1.3 Scope of this work

This thesis deals with the characterization of electrical contacts for phase change memory cells. Electrical contacts are an integral part of the phase change memory cell. The nature is expressed in terms of contact resistance  $R_{\rm C}$  and specific contact resistance  $\rho_{\rm c}$ . As the critical feature size F of semiconductor devices scales down into the (sub micrometer) nanometer regime, the physical size of electrical contacts in the device also decreases. This is because the scaling of the contact resistance approaches  $F^{-2}$  for small contacts [16]. Hence the relative contribution of the contact resistance increases more rapidly than the device resistance. In the case of a phase change memory cell,  $\rho_{\rm c}$  of the electrode to crystalline PCM is approximately  $7 \times 10^{-8} \ \Omega.{\rm cm}^2$  (as will be shown in the following chapters). This means that a square contact of 100 nm×100 nm results in a  $R_{\rm C}$  of 700  $\Omega$  per contact. This is a significant value when compared to the PCM line

resistance  $R_{\rm L}$ , which is adjusted to 2 k $\Omega$  by the geometry of the PCM layer. During reset operation, the impedance of the access device should be matched with the set resistance of the cell  $R_{\rm set}$ , for optimum power transfer. This includes the resistance of the crystalline line to be amorphized  $R_{\rm L}$  and the contact resistance  $R_{\rm C}$ , that acts as a parasitic resistance. During set operation,  $V_{\rm TH}$  depends on the voltage across the amorphous region. For other technology nodes the resistance of the line cell should be adjusted to the accompanying transistor. This includes the geometry and the material of the line cell  $R_{\rm L}$  itself and the contact resistance  $R_{\rm C}$ . With the knowledge of  $\rho_{\rm c}$ , the contacts in a PCRAM cell can be engineered for optimum device performance, not to be a limiting parameter for the performance of next generation CMOS devices. For other than the line cell configurations, the  $R_{\rm C}$  for electrode to amorphous PCM are also of importance [17]. Moreover the influence of thin (down to 5 nm) PCM layers and the behavior under high frequencies (user) conditions further improve the understanding of the memory cells.

Although important for electrical performance optimization and scaling of phase change memories, very little attempts have been reported to understand the electrode to PCM contact properties [17][18]. The aim of this work is to gain a microscopic and macroscopic understanding of electrode to PCM contacts. As the PCM technology scales in dimension and incorporate different material and device architectures, improvement in performance demands the understanding of the PCM and its contacts. In this thesis the following subjects will be discussed:

- What measurement structures are suitable to characterize electrode to PCM contacts?

- What contact resistivity values are achievable for PCRAM cells?

- What is the charge transport mechanism at the electrode to PCM interface?

- What is the contact resistance value at the operating frequency of a PCRAM cell?

- What is the influence of parasitic current paths in test structures on the measured values?

#### 1.4 Outline of the thesis

In chapter 2 contact resistance and different measurement structures used in this research are introduced. Different types of interfacial charge transport mechanisms are briefly reviewed from a metal to semiconductor contact perspective. Measurements presented in the following chapters on metal to PCM contacts reveal similar properties.

In chapter 3 the different material parameters of the PCM like resistivity, mobility, carrier concentration and optical band gap are determined from electrical,

optical and Hall effect measurements. The knowledge of these parameters is essential along with the contact resistance values to establish the electrical conduction mechanisms at the contact.

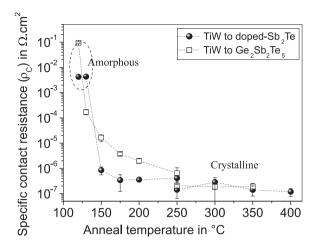

In chapter 4 the  $\rho_c$  extracted for TiW to doped-Sb<sub>2</sub>Te and Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> from two different measurement structures are compared. In the amorphous state of the PCM, these contacts exhibit a polarity dependence and temperature dependence. Based on the measurements with different electrodes and using a metal to semiconductor model, the interface barrier creation and charge transport mechanism at the contact are modeled with the presence of donor and accepter states in the PCM. In the last part of this chapter the extracted  $\rho_c$  values for different thicknesses of doped-Sb<sub>2</sub>Te layers are reported.

In chapter 5 a modified test structure and a novel data extraction procedure is presented that is suitable for electrical contact interface characterization with frequency. The relevance of high frequency (HF) measurements, design criterion and the steps involved in the fabrication of these test structures are described in the first part of this chapter. Measurements were performed on two different test structures up to 4 GHz. Based on these measurements, the contact is modeled with a resistance capacitance network. This method can separate the interface resistance from the interface capacitance values.

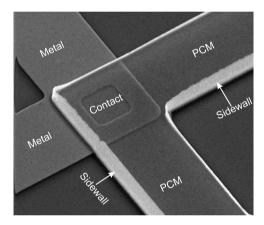

In chapter 6 the influence of parasitic current paths in the test structures on measured resistance is discussed. They lead to additional potential drops and higher measured resistance values. During pattering of the PCM layer, conducting re-deposited sidewalls are formed around the etched layer. In the first part, the presence of re-deposited sidewalls is experimentally characterized by resistance measurements on Van der Pauw structures. The impact of the formed sidewalls on contact resistance measurements and data extraction from these structures is shown. In the reset state of the PCRAM cell, in addition to the electrode to PCM interface, crystalline PCM to amorphous PCM interfaces are also present. In the second part of this chapter, test structures are presented to characterize the interfaces between crystalline and amorphous PCM. Attempts to characterize these interfaces were hindered by the formation of a non-uniform interface due to re-deposited residues and partial crystallization of the amorphous PCM. Details of these experiments with TEM evidence are presented.

Finally in the last chapter, the results are summarized from a PCRAM line cell perspective.

2

## Contact resistance methodology

This chapter introduces the contact resistance and the different measurement structures that are suitable for contact resistance characterization. In the first part, the contact resistance in a PCRAM cell and the parameters that determine the nature of this interface are presented. In section 2, interfacial barrier creation and the possible charge transport mechanisms at a metal to semiconductor is briefly discussed. Our results in Chapter 4 indicate that metal to phase change material contacts show similar properties as metal to semiconductor contacts. To cross the interface charge carriers have to overcome a potential barrier which creates an interfacial potential. Contact characterization is essentially the determination of this interfacial potential drop, and it is expressed in terms of contact resistance and specific contact resistance. Measurement structures that are suitable to characterize these interfaces are Kelvin resistor structures and Transfer Length Method structures. The theory and data extraction procedure from these test structures are discussed in section 3. In an electronic device during operation the memory cells will be accessed at a certain speed. Hence it is relevant to know the contact resistance value at its operating frequency. In the following section a modified test structure is presented which is suitable for contact resistance measurements with frequency. Each test structure has its own design rules, measurement range and limits. This knowledge is essential for proper selection of a test structure for accurate extraction of specific contact resistance values. This is discussed in the subsequent section.

#### 2.1 Contact resistance

In micro/nano electronic devices, a *contact* refers to the metallization layer applied to have a good electrical and physical contact with the functional layers in a (semiconductor) device. Through these contacts the current enters and leaves the device. Depending on the pattern of current flow to these contacts, they are classified into [19];

- Vertical contacts: The current flows vertically to the contact having a uniform current distribution.

- Horizontal contact: The current flows laterally to the contact. This leads to current crowding effects at the contact edges.

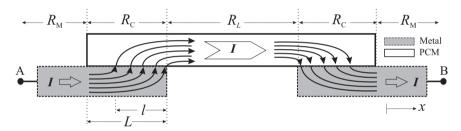

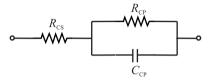

A PCRAM line cell as shown in Fig. 1.2 consists of a line of phase change material contacted with metal electrodes on both ends. The schematic cross section of this cell with a current, I flowing from A to B is shown in Fig. 2.1. The contacts formed in these cells are horizontal contacts. The total resistance

Figure 2.1: Schematic cross section of a PCRAM line cell with the pattern of current flow.

between terminals A and B is then represented as:

$$R_{\rm AB} = 2R_{\rm M} + R_{\rm L} + 2R_{\rm C} \tag{2.1}$$

The value of the resistance of the metal electrode  $R_{\rm M}$  and resistance of the PCM between the metal electrodes  $R_{\rm L}$  is determined from the geometry of the cell and the sheet resistance values of metal and PCM.  $R_{\rm C}$ , the total resistance encountered as the current is forced from metal electrode to the PCM, can be determined from measurements on dedicated test structures.  $R_{\rm C}$  depends on [20][21]:

• Physical properties of the materials: At the contact in a thin surface layer of the materials, the charge carrier density differs from that of the bulk. This is due to the difference in the work function of the two materials at the contact or due to the presence of surface states.

- Process limiting factors: This could be due to the presence of a thin layer of conducting or non-conducting foreign matter or oxidation of the material or a chemical reaction at the interface.

- Current crowding: Due to geometrical effects, the presence of a contact alters the electric field and hence the current distribution in the vicinity of the contact. This change in current distribution introduces additional resistance to current flow.

The parameter describing the physical properties of the interface is defined as the intrinsic resistivity,  $\rho_i$ . The contact resistance  $(R_C)$  includes the contribution of intrinsic resistivity  $\rho_i$ , the portion of the metal below the interface and PCM above the interface, current crowding effects and the presence of any interfacial layer at the contact. In a real contact these possible contributions occur simultaneously<sup>1</sup> [20][21][23]. This leads to the term contact resistivity or specific contact resistance  $\rho_c$ . This value is related to  $R_C$  with the effective contact area (see eq. 2.9). Thus the electrical nature of a contact is characterized by contact resistance,  $R_C(\Omega)$  and specific contact resistance,  $\rho_c(\Omega.\text{cm}^2)$ . When evaluated at zero bias,  $\rho_c$  is an important figure of merit for transport characteristics at the barrier; defined as [24]:(Derivation in appendix A1)

$$\rho_{\rm c} = \left(\frac{\partial J}{\partial V}\right)_{V=0}^{-1} \tag{2.2}$$

$\rho_{\rm c}$  is considered as the figure of merit in case of *ohmic* contacts. It is independent of contact area and hence it is a convenient parameter to compare contacts of different size. This  $\rho_{\rm c}$  is used in this research.

## 2.2 Current transport at the interface

The general theory of equilibria [25] states that when two electronic conductors are in contact and in thermal equilibrium, the electrochemical potentials (Fermi level) must be the same in both conductors. Charge transfer takes place through the interface to bring the two Fermi energies into alignment. This creates an opposing dipole that prevents further charge transfer and the contact potential developed depends on the work function difference of the two materials. A space charge region is created in the semiconductor material close to the interface, which is depleted of mobile charge carriers. The charge on the surface of the metal is within the Thomas-Fermi Screening length ( $\approx 0.05$  nm) [26]. The extent of the space charge region into the semiconductor depends on the doping level. The existence of a barrier to charge carriers at the metal-semiconductor interface was independently proposed by Schottky [27][28][29] and Mott [30]. This charge

<sup>&</sup>lt;sup>1</sup>For metal to metal contacts treated by Holm [22] contact resistivity is the constriction resistance, where the interface and the bulk effects are not separated.

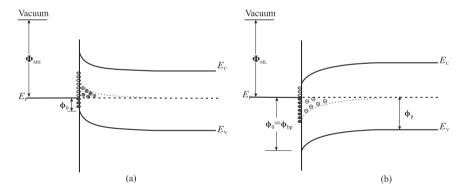

transfers across a metal to semiconductor (or a dielectric) interface, according to the Schottky model is governed by a barrier height  $(\phi_b)$ . This is the energy difference between the Fermi level and the majority carrier band edge at the interface, which is valence band maximum for p-type materials and conduction band minimum for p-type materials. For an ideal metal to semiconductor interface, i.e. one in which the interface is inert and without surface or induced interface states in the semiconductor, the barrier height measured relative to the Fermi level for metal to p-type  $(\phi_{bp})$  and p-type  $(\phi_{bp})$  semiconductors is given by [31]:

$$q\phi_{bn} = \Phi_{\mathcal{M}} - q\chi \qquad \& \qquad q\phi_{bp} = E_{\mathcal{g}} + q\chi - \Phi_{\mathcal{M}} \tag{2.3}$$

where,  $\chi$  is the electron affinity of the semiconductor measured form the bottom of the conduction band to the vacuum level and  $E_{\rm g}$  is the semiconductor band gap. This is referred as Schottky-Mott limit, by which the barrier height is determined by the metal work function<sup>2</sup>( $\Phi_{\rm M}$ ).

The current transport at a metal-semiconductor interface is mainly determined by majority carriers crossing the barrier. The total current through the interface at equilibrium condition constitutes of a thermionic emission component and a tunneling component. The relative magnitude of these two cases at an interface depends on the temperature T and carrier concentration  $N_{\rm C}$ . The carrier concentration at which the conduction mechanism at the contact changes from one to other is based on the characteristic energy  $E_{00}$ , a material constant that determines the tunneling probability.  $E_{00}$  is defined as [32]:

$$E_{00} = \frac{qh_p}{4\pi} \sqrt{\frac{N_C}{m^* \epsilon}} = 18.5 \times 10^{-12} \sqrt{\frac{N_C}{(m^*/m)\epsilon_r}}$$

(2.4)

where,  $h_{\rm p}$  is the Planck's constant, q is the electronic charge,  $m^*$  is the effective mass of the tunneling electron, m is the free electron mass, and  $\epsilon_{\rm r}$  is the dielectric constant of the semiconductor. The ratio  $k_bT/E_{00}$  is a measure of thermionic process in relation to tunneling. In the case of materials with [33];

- low carrier concentration,  $k_bT >> E_{00}$  and thermionic emission (TE) process dominates the current transport through the interface.

- large carrier concentration,  $k_bT \ll E_{00}$  and current transport is by tunneling or field emission (FE) through the barrier.

- In between,  $k_bT \approx E_{00}$ , current flows due to electrons with energy tunneling through the mid section of the potential barrier. This is called thermionic field emission (TFE).

$<sup>^2 \</sup>text{Work function } \Phi_{\text{M}}$  is the energy difference between the vacuum energy level and the Fermi energy level. Vacuum energy level represents the energy at which the electron can be free of the material and could be emitted away from the solid.  $\Phi_{\text{M}}$  is related to the potential  $\phi_{\text{M}}$  by the relation  $\Phi_{\text{M}}=q\phi_{\text{M}}$

The current transport at a contact is primarily described by TE theory if the barrier height is larger than  $k_bT$ , and the carriers are thermally excited over the barrier. Assuming Maxwell-Boltzmann approximation, the current density (J) at the metal to semiconductor junction, without image force lowering is expressed as [31]:

$J = \left[ A^* T^2 \exp\left(\frac{-q\phi_b}{k_b T}\right) \right] \left[ \exp\left(\frac{qV_a}{k_b T}\right) - 1 \right]$  (2.5)

The first term in this is saturation current density  $J_{\rm ST}$ , which is dependent on the zero bias barrier height. Using eq. 2.2,  $\rho_{\rm c}$  at zero bias is calculated for thermionic emission model as [24]:

$$\rho_{\rm c} = \frac{k_b}{qA^*T} \exp\left(\frac{-q\phi_b}{k_bT}\right) \tag{2.6}$$

As evident from this equation for TE model  $\rho_c$  decreases exponentially with decreasing  $\phi_b$  and increasing temperature. At the same time  $\rho_c$  is independent of  $N_{\rm C}$  and voltage bias (unless image force lowering is considered which will lowers  $\phi_b$ ).

At high  $N_{\rm C}$  the extent of the space charge region in the semiconductor will also be small such that quantum mechanical tunneling of the charge carriers takes place through the interface. In this case the current through the interface is proportional to the quantum transmission coefficient multiplied by the occupation probability. With current transport dominated by tunneling,  $\rho_{\rm c}$  is expressed as [31]:

$$\rho_{\rm c} = \exp\left(\frac{q\phi_b}{E_{00}}\right) = \exp\left[\frac{4\pi\sqrt{\epsilon m^*}}{h_p}\left(\frac{\phi_b}{\sqrt{N_{\rm C}}}\right)\right] \tag{2.7}$$

In the tunneling regime  $\rho_{\rm c}$  is independent of temperature, but depends strongly on  $N_{\rm C}$  and tunneling effective mass. The tunneling probability increases with  $N_{\rm C}$ , making the potential barrier thinner and easier to tunnel through.

Thermionic field emission (TFE) is the situation that bridges the two limits. In this case the thermally excited carriers reach an energy where the barrier is reasonably narrow for tunneling to occur. With TFE,  $\rho_c$  is expressed as [33]:

$$\rho_{\rm c} = \exp\left(\frac{q\phi_b}{E_{00}\coth\left(\frac{E_{00}}{k_bT}\right)}\right) = \exp\left[\frac{4\pi\sqrt{\epsilon m^*}}{h_p}\left(\frac{\phi_b}{\sqrt{N_{\rm C}}\coth\left(\frac{E_{00}}{k_bT}\right)}\right)\right]$$

(2.8)

In this case,  $\rho_{\rm c}$  depends on temperature,  $N_{\rm C}$ , tunneling effective mass, and on the  $\phi_b$ .

A good ohmic contact has no potential barrier at the interface, hence  $\rho_c$  should be sufficiently small to exhibit a linear or quasi-linear current-voltage (I-V) characteristic. For devices, a contact is also considered ohmic, if the voltage drop across the contact is small compared to the voltage drop across the active region of the device [34]. In the case of dedicated test structures, metal-semiconductor contacts with a high carrier concentration in the semiconductor, the depletion

region width becomes small, such that the electrons can tunnel through the barrier in addition to thermionic emission process [35]. This added component of tunneling current reduces the voltage across the contacts, resulting in an *ohmic* contact [33]. Similar case exists for electrode to crystalline PCM contacts. Ideal interfaces are homogeneous, intimate, abrupt, and free from any structural or chemical defects. Our measurements indicated that structural defects exist in the PCM at the interface. This leads to deviation of the metal to PCM interface properties form an ideal metal to semiconductor interface. These non idealities will be treated in the subsequent chapters.

#### 2.3 DC contact resistance measurement structures

Metal-semiconductor contacts had been identified and researched for the past two centuries are now commonly referred as Schottky-barrier devices in honour of Walter H. Schottky [36] who formulated the first acceptable theory of rectification at these contacts [27][28][29]. For electrical conduction at these contacts charge carriers need to pass the potential barrier at the interface. Depending on the nature of the interface, as described in the previous section this results in an interfacial potential drop. Characterization of the contacts is essentially determination of this interfacial potential drop. This interfacial potential drop is separated from the potential drop in the device and is expressed as contact resistance,  $R_{\rm C}$ . This section describes the test structures suitable for interface characterization, and the data extraction procedure to obtain  $\rho_c$  values from these structures. Direct measurement of individual contact resistance is possible using a four-terminal Kelvin resistor structure [37]. A technique to measure planar contact resistance associated with metal-semiconductor interface was developed by Shockley [38]. In this approach, current is constrained to flow from one metal contact to the semiconductor, through which it flows for a length and then enters into the second metal contact. From the associated voltage drop and knowledge of the sheet resistance  $R_{\rm SH}$  of the semiconductor layer the contact resistance is estimated. A model describing planar contacts on monolithic structure was developed by Kennedy and Murley [39]. This model shows large current crowding effects at the contacts, which was refined independently using transmission line equations by Berger [40] and Murrmann and Windmann [41] [42][43]. When the current flows from PCM to metal or vice versa at the contact it encounters  $R_{\rm SH}$  and  $\rho_{\rm c}$ , choosing the path of least resistance. This leads to current crowding at the contact which results in a suitable parameter, the transfer length l, from which the  $\rho_{\rm c}$  is extracted. The  $\rho_{\rm c}$  extraction model based on this parameter is known as the transfer length method (TLM). In the case of the measurement structures based on this model, contact resistance determination deals with a difference rather than absolute values. Various other two terminal methods like twin contact method, extrapolation method, differential method and contact chains or contact strings [20][44] also exist for contact resistance determination. In this work we focus on Kelvin resistor and transfer length method structures.

#### 2.3.1 Kelvin resistor structures

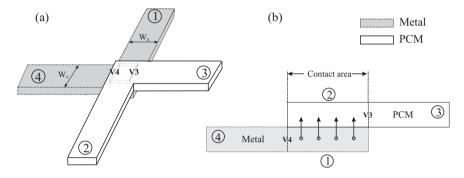

The Kelvin resistor is a planar structure suitable for interfacial contact resistance measurements with minimum parasitic resistance interference [37]. In the Kelvin measurement, the current and voltage at the contact are measured using a four terminal force-sense configuration. The schematic of a Kelvin resistor structure and its cross section along the contact area is shown in Fig. 2.2. The structure consists of a metal segment and a PCM segment, with an overlap area (A) which serves as the contact.

Figure 2.2: Schematic representation (not to scale) of the Kelvin resistor structure (a), cross-section (b) along the contact region.

To measure the metal to PCM contact resistance, a current is forced from the metal to PCM (1 to 2) and the voltage is measured orthogonal to the direction of current flow (3 and 4). This allows measurement of the average voltage, V (is V4-V3) at the contact, from which the contact resistance ( $R_{\rm C}$ ) is calculated. This four terminal measurement avoids the probe to contact pad resistance and the resistance of the current and voltage taps up to the contact region from the measured resistance. The specific contact resistance,  $\rho_{\rm c}$  is then calculated from  $R_{\rm C}$  as:

$$\rho_{\rm c} \left[ \Omega.{\rm cm}^2 \right] = R_{\rm C} \times A \tag{2.9}$$

Misalignment of the layers at the contact could lead to a contact width which is different from the tap width. This results in a resistive drop due to current flow in the periphery of the contact area. This lateral current crowding strongly affects the measurement accuracy of  $\rho_c$  which is appreciably visible in the range lower than  $10^{-6} \Omega \cdot \text{cm}^2$  [45][46]. In this case the extracted  $\rho_c$  using eq. 2.9 will be over estimated due to the current crowding effects around the contact. Two-dimensional numerical simulations were required to extract  $\rho_c$ , taking into account the current crowding in the overlap region around the contact area [45][47][48]. This misalignment tolerance can be avoided by fabricating the same structures

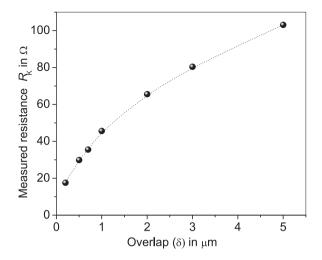

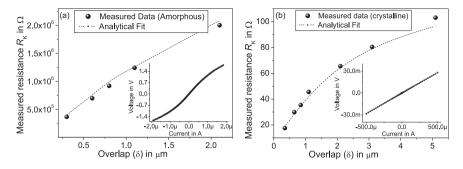

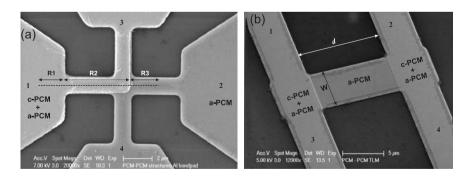

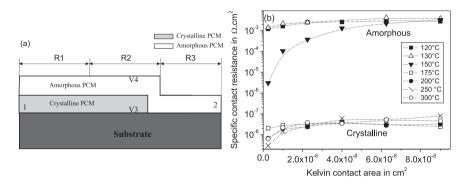

with a defined contact area (A) in the dielectric surrounded by a well defined overlap region  $(\delta)$ . These structures are basically the same Kelvin resistor structures. They are known as cross-bridge Kelvin resistor (CBKR) structures [48]. The SEM image of such a CBKR structure with a contact area (A) and an overlap length  $(\delta)$  is shown in Fig. 2.3(a), the schematic cross-section is shown in Fig. 2.3(b). As the current flows through these structures, it creates a potential drop in the interfacial contact region as well as in the  $\delta$  region. The measured resistance  $(R_{\rm K})$  consist of two components; one due to the voltage drop at the actual contact,  $R_{\rm C}$ , and the other due to the voltage drop due to current flow around the contact in the  $\delta$  region,  $R_{\rm D}$ . The first component,  $R_{\rm C}$  depends on  $\rho_{\rm c}$  the contact area A, while the second component,  $R_{\rm D}$  depends on the geometry of the structure.

Figure 2.3: CBKR structure showing the metal (TiW) and the PCM segments (a) Top view SEM image and (b) cross section view. The contact area and overlap length  $(\delta)$  between the two layers is also shown.

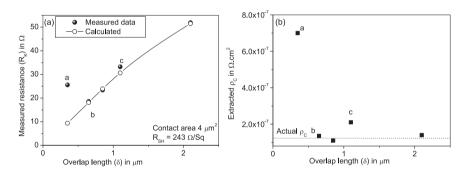

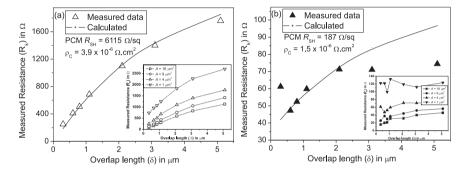

The change in  $R_{\rm K}$  of the CBKR structures with  $\delta$ , for given contact area is shown in Fig. 2.4. To determine  $\rho_{\rm c}$  accurately from these CBKR measurements, the contribution of  $R_{\rm D}$  needs to be eliminated from  $R_{\rm K}$ . The geometrical dependence of the overlap region to the total measured resistance is given by [49]:

$$R_{\rm K} = R_{\rm C} + R_{\rm D} = \frac{\rho_{\rm c}}{A} + \frac{4R_{\rm SH}\delta^2}{3W^2} \left[ 1 + \frac{\delta}{2(W - \delta)} \right]$$

(2.10)

Using eq. 2.10,  $\rho_c$  is extracted numerically or graphically with the knowledge of the geometrical parameters of the CBKR structure and  $R_{\rm SH}$  of the PCM layer.

#### 2.3.2 Transfer Length Method (TLM) structures

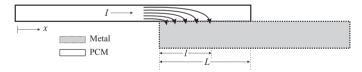

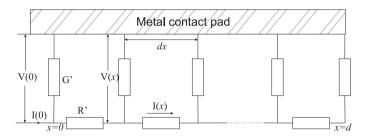

In the case of a lateral contact a current I, travelling from the metal into the PCM will generate a voltage drop at the metal to PCM interface. At each point at the contact the current branches through the contact and through the PCM. This is schematically shown in Fig. 2.5. The potential distribution at the contact is determined from  $R_{\rm SH}$  and  $\rho_{\rm c}$ , which is electrically modeled as a resistive network

Figure 2.4: Change in  $R_{\rm K}$  with  $\delta$  for a fixed contact area.

[50][44]. The current in the PCM decreases exponentially with the distance. The related voltage distribution under the contacts is given by [42][34]:

$$V(x) = V_0 \frac{\cosh\left[\left(L - x\right)/l\right]}{\sinh\left(L/l\right)} \approx V_0 \exp\left(-x/l\right)$$

(2.11)

Where  $V_0$  is the voltage at the leading edge of the contact, L is the length of the contact, l is the contact current transfer length and x indicates the direction of current flow.

Figure 2.5: Current transfer at a metal to PCM interface showing current crowding at the leading edge of the contact.

The contact parameters can be extracted by solving the differential current and the voltage equations describing the transmission line equivalent circuit of the contact [41][40][51]. The sheet resistance of the metal and the PCM and the interfacial resistance at the contact region have to be taken into account [42]. Assuming sheet resistance of the PCM much larger than that of the metal, the characteristic length of current transfer l at the contact is defined as [52]:

$$l = \sqrt{\frac{\rho_{\rm c}}{R_{\rm SH}}} \tag{2.12}$$

This is also defined as the "1/e" distance of the voltage curve represented by eq. 2.11 [44]. For contacts with L >> l, all the current will be transferred over a distance L >> 5l [42][39]. In TLM structures, the method to extract the contact resistivity is based on determining the value of l.  $\rho_c$  is then extracted using eq. 2.12. Different layouts for TLM structures have been developed: linear-TLM structure [41][40][53], circular-TLM structure [54], and Scott-TLM structures [55].

#### Linear TLM

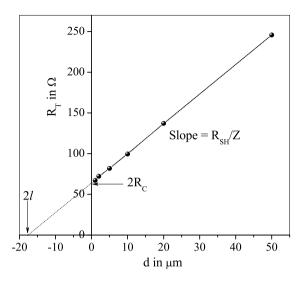

The linear-TLM structure consists of identical contacts with different spacing  $d_i$  (see Fig. 2.6). To determine the contact parameters, resistance measurements

Figure 2.6: Schematic layout of a liner-TLM structure.

are performed between adjacent metal pads. A current is forced from one metal pad through the PCM layer to the other metal pad using a pair of probes. The corresponding voltage drop is measured using a second pair of probes. Assuming an identical contact resistance for all contacts, the total measured resistance ( $R_{\rm Ti}$ ) between two metal pads is expressed as [50]: (derivation is presented in Appendix A2)

$$R_{\text{Ti}} = \underbrace{R_{\text{SH}} \left(\frac{d_{\text{i}}}{W}\right)}_{R_{\text{PCM}}} + \underbrace{\left(\frac{2l}{W}\right) R_{\text{SH}} \coth\left(\frac{L}{l}\right)}_{R_{\text{contact}}}$$

(2.13)

The sheet resistance of the metal is assumed to be negligible. If the length of the contact L is considerably larger than the transfer length l, then the equation 2.13 can be simplified to [19]:

$$R_{\rm Ti} \approx \frac{R_{\rm SH}d_{\rm i}}{W} + \frac{2R_{\rm SH}l}{W} = \frac{R_{\rm SH}d_{\rm i}}{W} + 2R_{\rm C}$$

(2.14)

For two metal pads with spacing  $d_1$  and  $d_2$ , the measured resistance is  $R_{\rm T1}$  and  $R_{\rm T2}$ . Using eq. 2.14,  $R_{\rm C}$  and  $R_{\rm SH}$  of PCM can be calculated as:

$$R_{\rm C} = \frac{R_{\rm T2}R_1 - R_{\rm T1}R_2}{2(d_1 - d_2)} \tag{2.15}$$

$$R_{\rm SH} = (R_{\rm T1} - R_{\rm T2}) \frac{W}{(d_1 - d_2)}$$

(2.16)

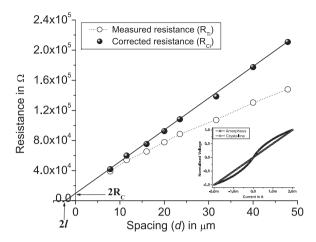

Figure 2.7: Measured resistance  $(R_{\rm T})$  with gap spacing d for linear-TLM. Estimation of l,  $R_{\rm C}$ , and  $R_{\rm SH}$  is also shown.

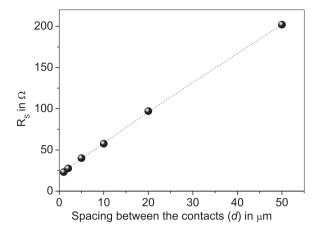

The resistance measured for different spacing and can be plotted versus d as shown in Fig. 2.7. This is essentially the plot of the linear relation as is in eq. 2.14. The contact parameters can also be extracted from the l which can be obtained graphically from this plot [53].  $R_{\rm SH}$  is the slope of the curve times width of PCM layer, W. From the intercept at d=0, two times the contact resistance ( $R_{\rm T}=2R_{\rm C}$ ) can be obtained and the intercept at  $R_{\rm T}=0$  gives two times the contact transfer length (-d=2l). From l, the  $\rho_{\rm c}$  is extracted using eq. 2.12.

#### Circular TLM

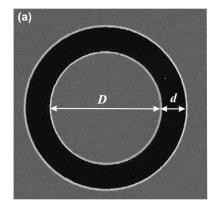

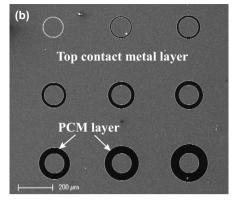

The circular-TLM structure is basically the same as the linear-TLM in terms of measurement and contact parameter extraction, but with a different layout. These structures consist of circular metal contacts with ring shaped spacing  $d_i$  [54]. A SEM image of a circular-TLM test structure with an inner circular contact pad of diameter, D and a ring shaped spacing d with the outer metal contact is shown in Fig. 2.8(a). Similar structures are available with different spacing, d (see Fig. 2.8 (b)).

For electrical contact resistance measurements a current is forced from the inner to the outer circular metal contact and the voltage drop between metal contacts is measured. Measurements on circular-TLM structures with different gaps result in different resistance values. The total measured resistance,  $R_{\rm T}$  between the inner and outer contact as derived from transmission line equation

Figure 2.8: Layout of (a) an individual circular-TLM structure, (b) circular-TLM structures used for measurements.

is given as [56][57][58]:

$$R_{\rm Ti} = \frac{R_{\rm SH}}{2\pi} \left[ \frac{l}{L_{\rm d} - d_{\rm i}} + \frac{l}{L_{\rm d}} + \ln\left(\frac{L_{\rm d}}{L_{\rm d} - d_{\rm i}}\right) \right]$$

(2.17)

where  $L_{\rm d}$  is (D/2)+d, and  $R_{\rm SH}$  is the sheet resistance of PCM. When the contact ring diameter to gap ratio (D>>d) is large, the ring geometry can be reduced to a standard linear-TLM model. This is done by including a correction factor to compensate for the difference between the linear and the circular ring layout. Without these correction factors the extracted  $\rho_{\rm c}$  will be underestimated [57]. For practical radii (up to 200  $\mu$ m) and gap spacing  $(4-48~\mu{\rm m})$ , the logarithmic term in eq. 2.17 can be evaluated using Taylor expansion and is rewritten as [56]:

$$R_{\rm Ti} \approx \left[ \frac{R_{\rm SH} d_{\rm i}}{Z_{\rm P}} + \frac{2R_{\rm SH} l}{Z_{\rm P}} \right] \times c = \left[ \frac{R_{\rm SH} d_{\rm i}}{Z_{\rm P}} + 2R_{\rm C} \right] \times c$$

(2.18)

where,  $Z_{\rm P}=2\pi(D/2)$  is the perimeter of the inner circular metal pad, and c is the correction factor:

$$c = \frac{D}{2d} \ln \left[ \frac{2L_{\rm d}}{D} \right] \tag{2.19}$$

To extract the contact parameters the measured  $R_{\rm T}$  values are converted to its equivalent linear model by application of this correction factor. Then l and  $R_{\rm SH}$  values are extracted graphically by plotting the corrected measured resistance values with d. From l the  $\rho_{\rm c}$  is extracted using eq. 2.12.

#### Scott TLM

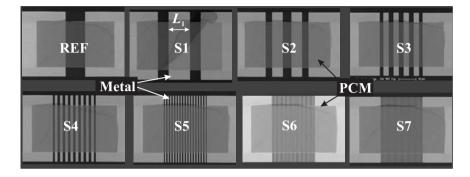

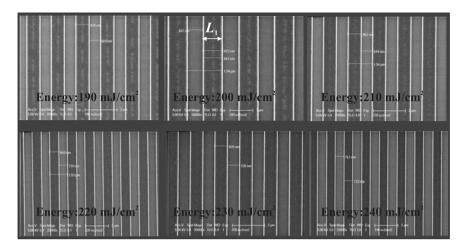

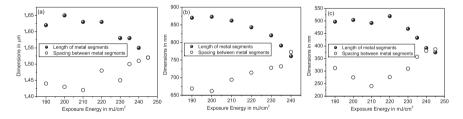

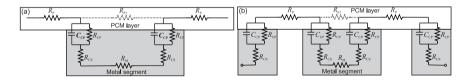

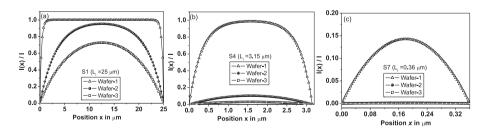

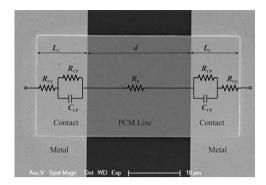

Scott-TLM test structures consist of a reference structure and structures with metal segments of varying length underneath the PCM layer. The reference structure consists of a PCM line without any metal segment. The top view SEM image

of the reference structure (REF) and the Scott structures (S1-S7) are shown in Fig. 2.9. Metal segments of equal length are repeatedly placed at equidistance between these two contacts such that: 1) the total length of PCM in all the structures is the same as in the reference structure and 2) the total lengths of PCM segments and the metal segments are the same. Two large metal to PCM contacts at the ends of the PCM line serve as the entry and exit contacts for the current. The number and width of the metal segments for each structure we used is given

Figure 2.9: Top view SEM image of reference structure (REF) and other Scott structures (S1-S7) showing the metal segments and PCM line.

in Table 2.1. A cross-sectional schematic of the Scott structure showing the PCM layer on top of the metal segment is shown in Fig. 5.9.

| Structure | Number $(n)$ | Length $L_{\rm i}(\mu{\rm m})$ |

|-----------|--------------|--------------------------------|

| REF       | 0            | 0                              |

| S1        | 1            | 25                             |

| S2        | 2            | 12.5                           |

| S3        | 4            | 6.25                           |

| S4        | 8            | 3.15                           |

| S5        | 16           | 1.57                           |

| S6        | 32           | 0.78                           |

| S7        | 64           | 0.39                           |

Table 2.1: Metal dimensions for different Scott-TLM structures

The measurement technique for these structures is by eliminating the resistance of the reference structure (REF) not interrupted by metal segments from the resistance of the structures (S1-S7) interrupted by one or more metal segments. As the structures have been designed to have equal PCM and electrode segments lengths, the difference between the reference resistance and the others

resistances is attributed to the total contact resistance,  $R_{\rm CT}$ . With the metal resistance negligible compared to the sheet resistance of the PCM layer  $R_{\rm SH}$ ;

$$R_{\rm CT} = R_{\rm Ti} - R_{\rm ref} \tag{2.20}$$

where  $R_{\text{Ti}}$  is the resistance of the structure interrupted by n metal segments, Rref is the resistance of the reference structure. From  $R_{\text{CT}}$ , the contribution of the contact resistance  $(R_{\text{C}})$  of the individual metal segments in a structure is expressed as:

$$R_{\rm C} = \frac{R_{\rm Ti} - R_{\rm ref}}{n} \tag{2.21}$$

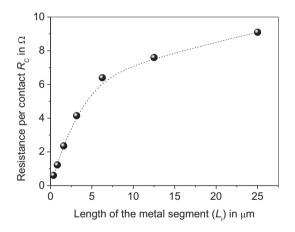

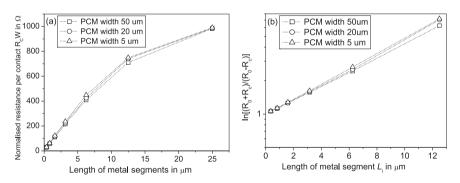

The change in  $R_{\rm C}$  with the length of the metal segment  $L_{\rm i}$  is shown in Fig. 2.10. With the knowledge of  $R_{\rm SH}$  and width of the PCM segment W,  $\rho_{\rm c}$  is then extracted from  $R_{\rm C}$  by fitting the measurements with the equation [55]:

$$R_{\rm C} = \frac{2\sqrt{\rho_{\rm c}R_{\rm SH}}\tanh(L_{\rm i}/2l)}{W}$$

(2.22)

Figure 2.10: Change in  $R_{\rm C}$  with length of the metal segments in the Scott structure.

When a current is forced through these Scott structures the current divides itself between the PCM layer and the metal segments, based on  $L_{\rm i}$  of the structure compared to l. The two limiting cases for these structures are:

- 1.  $L_{\rm i} << l;$  the current does not have enough length to enter the metal and hence the presence of metal has little or no effect on the measured resistance.

- 2.  $L_i >> l$ ; the current has enough length to completely enter the metal from the PCM, and flows through the metal before it goes back to the PCM.

In this case the metal segment shorts that part of the PCM resistance. At the same time it adds two metal to PCM contact resistances  $R_{\rm C}$  and the metal segment resistance. Applying this to eq. 2.22, the limiting case of this resistance can be expressed as;

$$R_{\rm C} \lim_{L_i > l} = R_0 = \frac{2\sqrt{\rho_{\rm c}R_{\rm SH}}}{W}$$

(2.23)

These two conditions can be understood by considering the fraction of the current I in the metal segment  $L_i$  as a function of the position x. With negligible metal resistance this is represented as [51]:

$$\frac{I(x)}{I} = \frac{\sinh(L_i/l) - \sinh(x/l) - \sinh((L_i/l) - x)}{\sinh(L_i/l)}$$

(2.24)

Since Scott structures are available with different metal lengths, the limiting condition for  $R_{\rm C}$  in eq. 2.23 can be applied to eq. 2.22 and can be expressed as [55]:

$$\frac{R_0 + R_C}{R_0 - R_C} = \exp\left(\frac{L_i}{l}\right) \tag{2.25}$$

From the slope of the plot of eq. 2.25 as a function of  $L_i$ , the contact transfer length l is calculated and  $\rho_c$  can be extracted.

#### 2.4 High frequency measurement structures

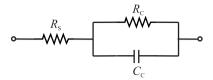

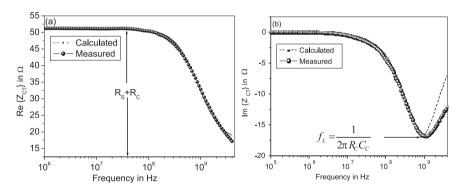

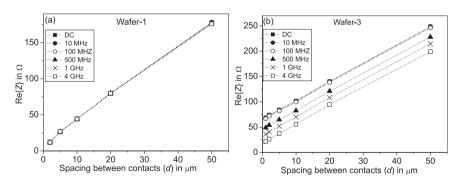

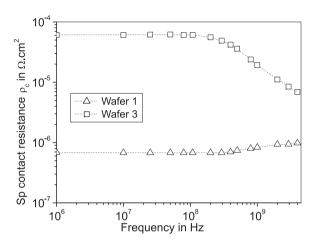

The test structures discussed so far are designed for contact resistance measurements at DC current and voltages. An embedded phase change memory cell will be accessed in a nano-second (ns) time scale during the operation of the device. They will be typically operated in the MHz frequency range. Hence the current and voltage at the contacts in this memory cell will not be static during operation. In this section a modified TLM test structure is presented which is proved to be suitable for High Frequency (HF) contact resistance measurements [59].

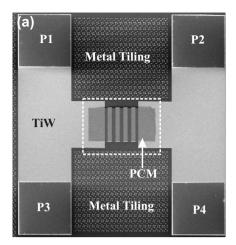

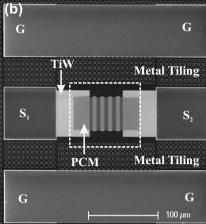

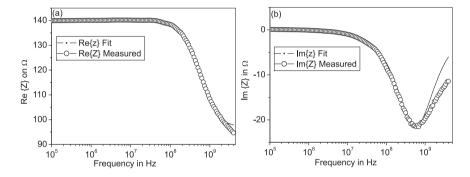

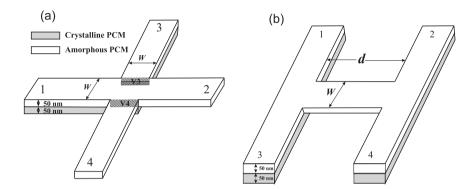

To be able to perform high frequency S-parameter measurements, test structures are designed in a Ground-Signal-Ground (GSG) configuration. Scott-TLM structures can be adapted in this GSG configuration. Identical test structures were fabricated on the same dies in the GSG and in the DC four terminal configurations to validate this HF approach. An SEM image of a Scott TLM structure with four metal segments in the GSG configuration and the DC configuration is shown in Fig. 2.11. From the measured S-parameters the real and the imaginary part of the differential impedance (Z) offered by each of the structures is calculated as [60]:

$$Z = Z_{\text{diff}} = Z_{11} - Z_{21} - Z_{12} + Z_{22} \tag{2.26}$$

Figure 2.11: SEM image of Scott-TLM structure with the PCM line intercepted by four TiW metal segments. (a) In the GSG configuration for HF measurements. (b) In the four bond-pad configuration for DC measurements.

From this measured  $Z_{\text{diff}}$ ,  $\rho_{\text{c}}$  is extracted with frequency. The design rules for the HF measurement structure, fabrication details, contact resistance measurements and data extraction are presented in Chapter. 5.

## 2.5 Comparison of the test structures

Both the Kelvin and TLM methods are suitable for accurate characterization of rectifying and ohmic contacts [57]. Since the underlying principles in the parameter extraction from these structures are different these structures are subject to different geometrical design criteria and measurement limits.

A Kelvin resistor structure employs a four terminal measurement and hence measures only one contact from which  $\rho_c$  can be extracted. The value of RC determined by this method is made up of several contributions, which bear direct relevance to the contact resistances in real device contacts [61]. The determination of  $\rho_c$  is based in the assumption of having a uniform contact interfacial layer. For non uniform layers  $\rho_c$  cannot be defined since it is not constant from point to point in the contact [62]. This is presented experimentally in detail in Chapter 6.2. A design criterion for Kelvin structures is that, for accurate  $\rho_c$  extraction the size of the contact area should be such that it is completely used for current transfer (less than 5l). Another source of error in CBKR structures is when they are designed with a relatively large overlap region compared to the contact area. This leads to a larger geometrical resistance and inaccurate estimation of  $\rho_c$  [63].

In the case of TLM structures, contact resistance determination deals with

difference values rather than absolute values. TLM structures are less sensitive to overlap region since these structures are based on the transfer length principle. It detects only the front contact potential [64]. Hence the design criterion for these structures is that contact length L should be greater than 5l. With L >> l, the current density at the contact is influenced only by the contact width W and not L. An advantage of TLM structures over Kelvin structures is that these structures can be adapted in the GSG configuration suitable for HF contact resistance measurements. Limitation of a linear-TLM and circular-TLM structures:

- The main limitation of TLM structure is that it is a differential measurement and the PCM resistance is measured along with the contact resistance. This limits the accuracy of data extraction to the errors in determining the geometrical values of d, W and L.

- If the metal resistance is not negligible compared to  $R_{\rm SH}$ , this results in an appreciable voltage drop within the contact metal layer [58]. This situation occurs for highly resistive or thin contact metal layers. In this case the metal no longer acts as an eqi-potential layer and hence in this case the transfer length approximation and model is not valid.

- The transmission line approximation also fails in the case when sheet resistance of the PCM at the contacts is different from the sheet resistance of PCM between the contacts [53][21].

The main advantage of a circular-TLM structure is that due to the circular geometry of this structure current can only flow from the central contact to the surrounding contact. Any isolation is not required. In the case of linear-TLM structures a parasitic current could flow from contact to contact in non-isolated regions [44]. Circular-TLM structures can be fabricated on blanket films using a relatively simple metal lift off process. They can be processed at a lower thermal budget [56][65].

In the case of a Scott TLM structures, most of the limitations of a linear-TLM are subdued. Sheet resistance of PCM at the contact and on the metal segments can be different from that between metal segments. In the case of high resistive metal, or thin metallic layers this resistance should be taken into account in the analytical model [50][51]. In these structures the width of the metal contact segment  $L_i$  need not be greater than the l. The limit of  $\rho_c$  that can be extracted depends directly on  $L_i$  relative to l. For commonly used lithography techniques these structures are suitable to measure metal to PCM contacts with  $\rho_c$  in the  $10^{-9} \Omega \cdot \text{cm}^2$  range, which was not possible from other TLM structures.

#### 2.6 Van der Pauw structures

The knowledge of the sheet resistance  $R_{\rm SH}$  of a PCM layer is important for  $\rho_{\rm c}$  extraction from CBKR test structures and for TLM structures. In addition the

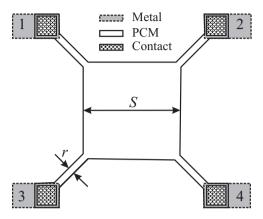

state of the PCM and its properties can also be identified from sheet resistance values. Van der Pauw structures of the type shown in Fig. 2.12 can be used for sheet resistance measurements of a thin film layer.

Figure 2.12: Schematic layout of a square Van der Pauw structure of side S.

To measure the sheet resistance of the layer, a current is forced from pad 1 to 2 and a voltage is measured at pad 3 and 4 in the structure. From this the resistance  $(R_{\rm V})$  of the layer is calculated. The length of the electrical contact (r) should be negligibly small compared to edge length of the structure (S). An advantage of this structure is that  $R_{\rm V}$  is independent of S. From  $R_{\rm V}$  the sheet resistance  $(R_{\rm SH})$  of the layer is obtained by using the geometrical factor, which is  $\pi/\ln(2)$  for a square structure [66][44]:

$$R_{\rm SH} = \frac{\pi}{\ln(2)} \times \frac{V}{I} \approx 4.53 \times \frac{V}{I}$$

(2.27)

$R_{\rm SH}$  is related to the Intrinsic layer resistivity  $(\rho)$  normalized with the thickness (h) as given by:

$$\rho = R_{\rm SH} \times h \tag{2.28}$$

The measurement structures for  $\rho_c$  determination are always accompanied by Van der Pauw structures to accurately measure the  $R_{\rm SH}$  values.

#### Phase change material properties

In this chapter, the relevant electrical and optical properties of two different classes of PCM are summarized. In the first part of this chapter, the temperature dependence of the resistivity of amorphous PCM is studied. From these measurements the amorphous to crystalline phase transition (crystallization) temperature, activation energy for conduction in the amorphous state and the temperature coefficient of resistance (TCR) in the crystalline state are determined. In the following section, the optical band gap and absorption coefficient for doped-Sb<sub>2</sub>Te is determined from ellipsometric measurements. In the last part of this chapter, the carrier type, the concentration and the mobility in the crystalline PCM is determined from Hall effect measurements. The knowledge of these parameters is essential for understanding and modelling the electrical charge transport mechanism at the metal to PCM interfaces.

## 3.1 Phase change resistivity measurements

In the application of PCM as embedded RAM, the electrical properties are of importance for write, erase and read operation. Phase change materials can be divided into two classes based on their crystallization mechanisms; nucleation dominated and growth dominated materials [67][8]. Phase change materials with composition on the tie-line GeTe-Sb<sub>2</sub>Te<sub>3</sub> in the phase diagram are classified as nucleation dominated materials. If these materials are sufficiently heated in the amorphous state crystallites nucleate in the layer, followed by growth of these nuclei over a small distance until they impinge on other crystallites [9]. These materials have a large nucleation probability, which occurs rather fast. Materials with a composition around the eutectic point Sb<sub>69</sub>Te<sub>31</sub> are growth dominated [8]. These materials have a lower nucleation probability, but once a crystallite is formed it grows faster. In the application for optical data storage, the crystallization initiates from the amorphous to crystalline interface, i.e. there is no nucleation needed [8]. In the application for memories; the Ovonic Unified Memory (OUM) cell uses a nucleation dominated material, in particular the composition Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> is known to yield good results, for memory line cells a growth dominated doped-Sb<sub>2</sub>Te material is preferred, doped with one or more elements from the series Ge, In, Ag and Ga [5].

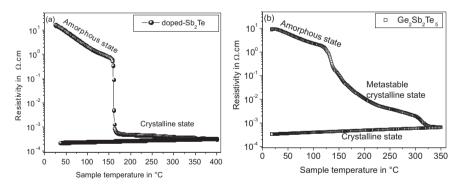

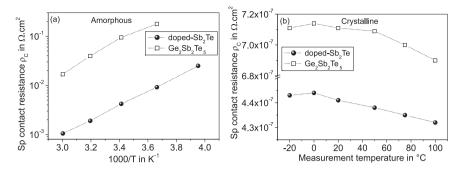

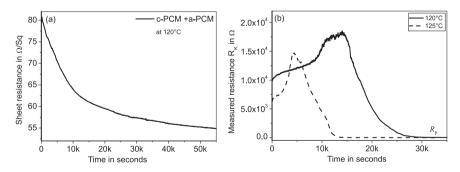

The change in resistivity of an amorphous thin film of doped-Sb<sub>2</sub>Te and  $Ge_2Sb_2Te_5$  with temperature is shown in Fig. 3.1. These measurements were performed on Van der Pauw structures in a  $N_2$  atmosphere with a temperature ramp rate of 5 °C/min.

Figure 3.1: Change in resistivity of amorphous (a) doped-Sb<sub>2</sub>Te and (b) Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> with thermal cycle.

At crystallization, at approximatly 150 °C, the resistivity of the layer decreases by more than three orders of magnitude. The temperature at which this transition occurs is called crystallization temperature. The crystallization temperature as such depends on the type of the phase change material, the temperature ramp rate, the surrounding layers and other parameters [8]. A ramp

rate of 5 °C/min for uncapped thin films of 20 nm, the crystallization temperature of doped-Sb<sub>2</sub>Te is 154 °C and for  $Ge_2Sb_2Te_5$  is approximately 130 °C [5].  $Ge_2Sb_2Te_5$  is observed to have a phase transformation in the crystalline state at a higher temperature of approximately 300 °C; it changes from the meta-stable fcc phase into the stable hexagonal phase [68]. This large contrast in resistivity between the amorphous and the crystalline state is employed to realize a PCRAM cell [5].

In the amorphous state, the resistivity/conductivity of the PCM follows an Arrhenius type exponential relation with temperature. This is expressed as [69]:

$$\sigma = \sigma_0 \exp\left(\frac{-E_{\rm A}}{k_b T}\right) \tag{3.1}$$

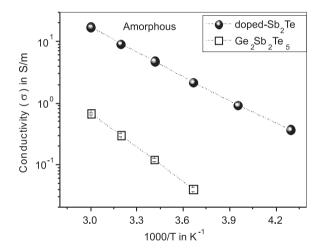

From eq. 3.1,  $E_{\rm A}$  can be calculated. The change in conductivity ( $\sigma$ ) of amorphous PCM layer with temperature in the range from -40 °C to 60 °C is shown in Fig. 3.2.

Figure 3.2: Change in  $\sigma$  with temperature measured for amorphous PCM layers.

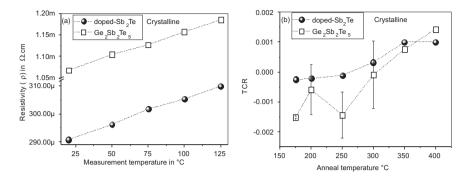

In the amorphous state, an  $E_{\rm A}$  for conductivity of 0.26 eV is calculated for doped-Sb<sub>2</sub>Te and 0.35 eV for Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>. For uncapped PCM layers, with a thickness in the range of 5 to 200 nm, the same crystallization temperature and  $E_{\rm A}$  is observed. In the crystalline state PCM shows metallic characteristics. A linear dependence of resistivity ( $\rho$ ) with temperature is observed as shown in Fig. 3.3(a). The calculated TCR of crystalline PCM after anneal at a temperature in the range 150 to 400 °C is shown in Fig. 3.3(b). In the crystalline state low TCR is observed for both PCM's. After anneal at a higher temperature the sign of the TCR changes. This transition depends on the annealing time and temperature. In the perfect crystalline state, a positive TCR is observed.

Figure 3.3: Change in  $\rho$  with temperature for crystalline PCM layers ( $\rho$  scale has a break in between) (b) the calculated TCR for crystalline PCM after anneal at temperatures in the range 150 to 400 °C.

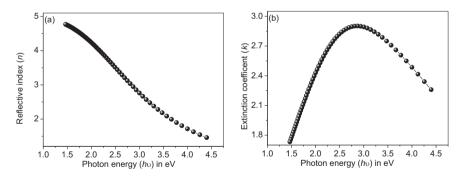

# 3.2 Optical properties of phase change materials (PCM)

The first commercial application of PCM for data storage is in CD and DVD rewritable. Write, erase and readout of data are done optically. For light of a specific wavelength  $(\lambda)$  the optical constants are expressed as the complex refractive index, expressed as n+jk, where n is the reflective index and k is the extinction coefficient. These optical constants of the material are determined from optical transmission and reflection ellipsometric measurements. The change in n and k values with photon energy,  $E_{\rm P}$  for doped-Sb<sub>2</sub>Te in the amorphous state is shown in Fig. 3.4. The reported n and k values for similar PCM exhibits identical

Figure 3.4: Change in the n and k value with photon energy for doped-Sb<sub>2</sub>Te in the amorphous state.

behavior in this wavelength range [70][71][8].

If a light beam with intensity  $I_0$  propagates over a distance x in the material,

then the intensity decreases to I, which can be expressed as [44]:

$$I = I_0 \exp\left(-\alpha x\right) \tag{3.2}$$

where,  $\alpha$  is the absorption coefficient of the material. With the knowledge of the optical constants, the absorption coefficient  $\alpha$  of a material can be calculated.  $\alpha$  is related to k as:

$$\alpha = \frac{4\pi k}{\lambda} \tag{3.3}$$

These optical properties of the PCM play an important role in the experimental section in Chapter 4.

The optical band gap,  $E_{\rm g}^{\rm opt}$  of a material is determined by the onset of optical absorption that occurs when the photon energy of the incident light just equals the energy separation of the highest occupied electron states in the valence band and the lowest empty states in the conduction band. Photons with energy greater than this energy separation are absorbed. Light with energy less than the bandgap will be transmitted or reflected. Hence  $E_{\rm g}^{\rm opt}$  is determined by measuring  $\alpha$  with  $E_{\rm P}$ , which is related as [8]:

$$\alpha h \nu = (\text{constant})(h\nu - E_{\text{g}}^{\text{opt}})^r$$

(3.4)

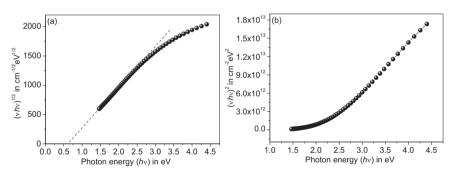

In the case of indirect band-gap materials r=2 (Tauc plot), or for direct gap materials r=1/2. The plot of  $(\alpha h\nu)^{1/2}$  with  $E_{\rm P}$  and  $(\alpha h\nu)^2$  with  $E_{\rm P}$  for doped-Sb<sub>2</sub>Te in the amorphous state is as illustrated in Fig. 3.5(a) and Fig. 3.5(b) respectively.

Figure 3.5: (a) Plot of  $(\alpha h \nu)^{1/2}$  with  $E_{\rm P}$  for amorphous doped-Sb<sub>2</sub>Te. of 0.6 eV is calculated from this plot. (b) Plot of  $(\alpha h \nu)^2$  with  $E_{\rm P}$

The relation with r of 2 is valid for chalcogenide materials indicating that these are indirect band-gap materials [72]. The calculated for doped-Sb<sub>2</sub>Te in the amorphous state is 0.6 eV.  $Ge_2Sb_2Te_5$  is reported to be an indirect gap material with a of 0.7 eV in the amorphous state and 0.5 eV in the crystalline state [8][73].

## 3.3 Hall effect measurements on PCM

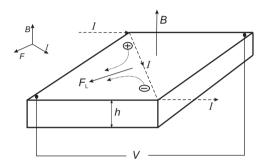

In this section the carrier concentration  $N_{\rm C}$ , mobility  $\mu$ , and polarity of the charge carrier (n-type or p-type) of crystalline PCM are determined from Hall effect measurements. The Hall effect [74] arises due to the existence of Lorentz force, which is the combination of electric force and magnetic force. When the charge carriers involved in the conduction, move along an electric field  $\vec{E}$  with a speed  $\vec{v}$  and with a direction perpendicular to an applied magnetic field  $\vec{B}$ , they experience a magnetic force  $(q\vec{v}\times\vec{B})$  acting normal to both directions. This is schematically represented in Fig. 3.6.

Figure 3.6: Schematic illustration of a Hall bar, showing the direction of B, I and the resulting  $F_{\rm L}$ .

The resulting Lorentz force  $\vec{F}_{L}$ , on the charge carriers due to the electromagnetic field is given by the vector representation [31][44]:

$$\vec{F}_{L} = q(\vec{E} + \vec{v} \times \vec{B}) \tag{3.5}$$

This internal force deflects the charge carriers generating an electric field within the layer. The polarity/direction of this field is determined by the nature of the majority charge carrier involved in conduction. Given the direction of magnetic field B and a positive current I as illustrated in Fig. 3.6, positive charge carriers are deflected to the left side (direction of  $\vec{F}_{\rm L}$ ). This result in a more positive potential at this half compared to the right half. The induced Hall field will be diagonally from the left corner to the right corner. In the case of electrons, the potential at the left side becomes more negative due to localization of electrons. This results in an opposite Hall field. Assuming an energy independent scattering mechanism, the induced Hall field, expressed as the Hall voltage,  $V_{\rm H}$ , is [44]:

$$V_{\rm H} = \frac{BI}{qhN_{\rm C}} \tag{3.6}$$

where h is the thickness of the layer, q is the elementary charge and  $N_{\rm C}$  is the

carrier concentration. From this, the Hall coefficient  $R_{\rm H}$  is derived as:

$$R_{\rm H} = \frac{HV_{\rm H}}{BI} \tag{3.7}$$

The charge carrier density in the layer is then expressed as:

$$N_{\rm C} = \frac{1}{qR_{\rm H}} \tag{3.8}$$

Assuming that only one type of carriers involved in the conduction, the electrical conductivity  $\sigma$  of the layer, is related to the electrical mobility  $\mu$  of the charge carriers in the layer by:

$$\sigma = q\mu N_{\rm C} \tag{3.9}$$

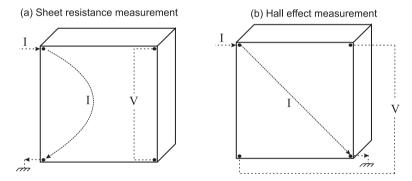

Hall effect measurements were performed on Van der Pauw structures, used for sheet resistance measurements [66]. The electrical connections of a square Van der Pauw structure for sheet resistance measurements and for Hall effect measurements are shown in Fig. 3.7.

Figure 3.7: Schematic of a square Van der Pauw structure in the sheet resistance measurement and Hall effect measurement configuration.

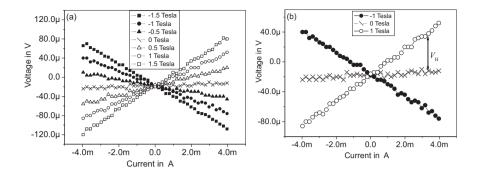

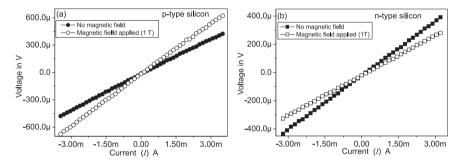

To perform Hall measurements, a current I is forced through the layer and the resulting voltage, V is monitored with and without magnetic field. To check the symmetry, these measurements were performed with positive and negative currents and with magnetic field in opposite directions. The measured I-V characteristics with different B for crystalline doped-Sb<sub>2</sub>Te are shown in Fig. 3.8(a).

The measured voltage is symmetrical and it increases with I and B. Fig. 3.8(b) shows the measurements on doped-Sb<sub>2</sub>Te; without magnetic field and with a magnetic field of 1 Tesla only (applied in opposite directions). The difference in voltage measured with and without magnetic field is the Hall voltage ( $V_{\rm H}$ ). For a fixed positive I through the layer, V increases with the application of a positive B. This implies that the charge carriers in doped-Sb<sub>2</sub>Te in the crystalline

Figure 3.8: Change in measured voltage with I and B for crystalline doped-Sb<sub>2</sub>Te.

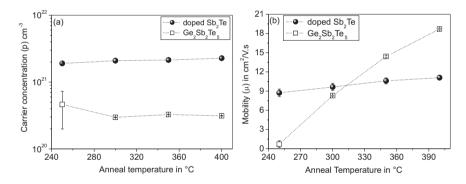

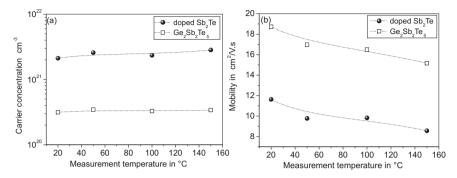

state are positively charged. Similar measurements performed on doped-Sb<sub>2</sub>Te and Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> samples annealed at different temperatures in the range from 250 °C to 400 °C also show p-type conduction. From these measurements  $V_{\rm H}$ ,  $N_{\rm C}$  and  $\mu$  are calculated using eq. 3.6 to eq. 3.9. These calculated  $N_{\rm C}$  and  $\mu$  values for both crystalline PCM materials are shown in Fig. 3.9. The  $N_{\rm C}$  values for doped-

Figure 3.9: Change in  $N_{\rm C}$  and  $\mu$  with anneal temperature.

Sb<sub>2</sub>Te and Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> remain constant upon annealing up to 400 °C. The  $N_{\rm C}$  for doped-Sb<sub>2</sub>Te is approximately  $2\times 10^{21}$  cm<sup>-3</sup>. This is one order of magnitude higher than that of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> ( $\approx 5\times 10^{20}$  cm<sup>-3</sup>). Our measured values for Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> agree well with the reported values [8][73]. The calculated  $\mu$  increases upon annealing at higher temperatures, as shown in Fig. 3.9(b). This increase in  $\mu$  is more pronounced for Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>. The value of  $\mu$  and  $N_{\rm C}$  are related to the resistivity by eq. 3.9. Hence the observed decrease in resistivity upon annealing is due to the increase in the mobility of the charge carriers rather than a higher  $N_{\rm C}$  [75]. In this case during heating crystallites grow and the scattering of the charge carriers at the grain boundaries decreases [68]. This results in an increased mobility [8].

3.4 Summary 33

Fig. 3.10 shows the change in the  $N_{\rm C}$  and  $\mu$  with measurement temperature for crystalline doped-Sb<sub>2</sub>Te and Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>.  $N_{\rm C}$  hardly changes with temperature, but  $\mu$  decreases slightly with temperature.

Figure 3.10: Change in  $N_{\rm C}$  and  $\mu$  with measurement temperature.

Measurements on high resistive samples in the amorphous state of the PCM show large experimental errors. This limits measurements on crystalline PCM only. In addition, use of higher magnetic field can mitigate this problem. Finally, to confirm the measurement results and to calibrate the Hall effect measurement setup, p-type and n-type silicon samples with a known  $N_{\rm C}$  were fabricated and measured. The details are given in Appendix A3.1.

## 3.4 Summary

The electrical properties of growth dominated doped  $\mathrm{Sb_2Te}$  and nucleation dominated  $\mathrm{Ge_2Sb_2Te_5}$  were investigated. When heated at a ramp rate of 5 °C/minute amorphous doped-Sb2Te crystallizes at 150 °C and  $\mathrm{Ge_2Sb_2Te_5}$  at around 130 °C. In the amorphous state both the PCM's exhibit an exponential dependence with temperature with an activation energy of 0.26 eV for doped-Sb<sub>2</sub>Te and 0.35 eV for  $\mathrm{Ge_2Sb_2Te_5}$ . The calculated optical band gap for doped-Sb<sub>2</sub>Te from ellipsometric measurements is 0.6 eV. In the crystalline state, an almost zero TCR is observed for both the PCM with p-type conduction. The calculated carrier density form Hall effect measurements is  $2 \times 10^{21}$  cm<sup>-3</sup> for doped-Sb<sub>2</sub>Te and  $5 \times 10^{21}$  cm<sup>-3</sup> for  $\mathrm{Ge_2Sb_2Te_5}$ . When annealed at a higher temperature, in the crystalline state the carrier concentration remains constant while the mobility increases.

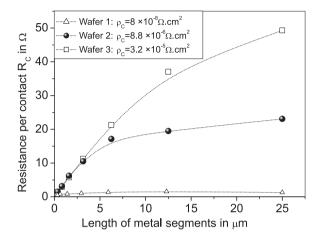

4

## Electrical characteristics of electrode to PCM contacts

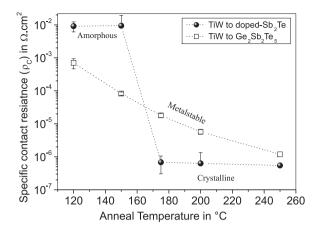

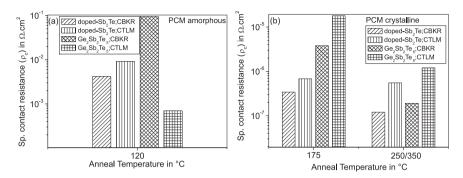

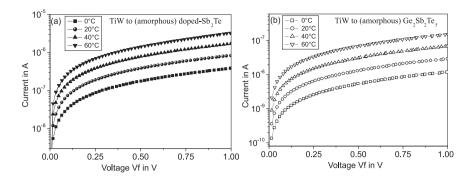

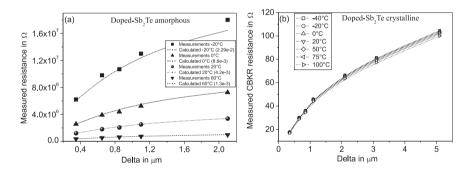

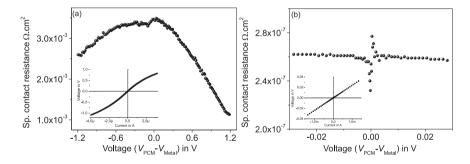

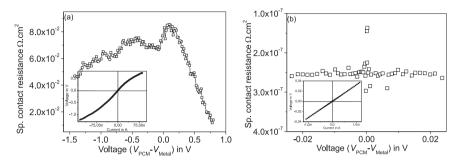

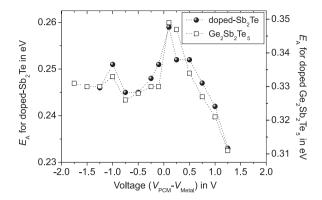

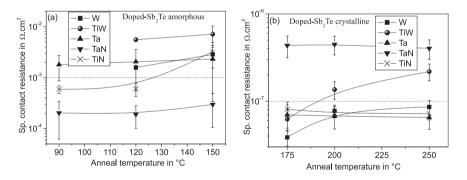

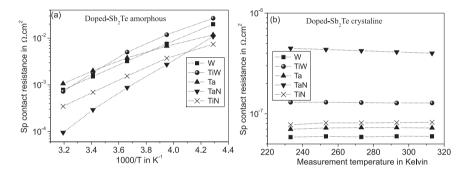

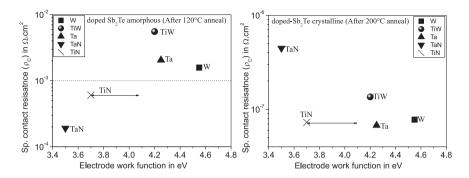

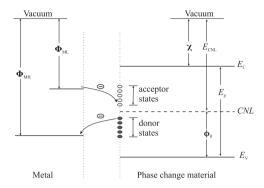

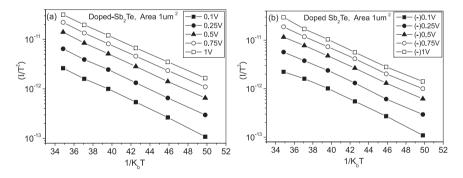

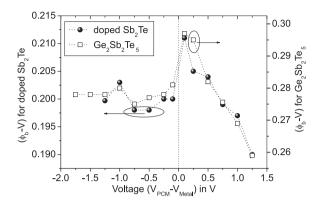

The aim of this chapter is to provide the reader with a complete understanding of contacts for metal to PCM in the amorphous and in the crystalline states. The first step in the understanding of these contacts is to accurately determine the electrical contact resistance. Dedicated test structures were fabricated from which the contact resistance is electrically determined. This measured value is expressed in terms of specific contact resistance  $\rho_c$ , which is a suitable parameter to compare different contacts. The next level of understanding of these contacts is to physically model the charge transport mechanism, based on the measured values.